# DynaBurst: Dynamically Assemblying DRAM Bursts over a Multitude of Random Accesses

Mikhail Asiatici and Paolo lenne

Processor Architecture Laboratory (LAP)

School of Computer and Communication Sciences

EPFL

FPL 2019, Barcelona, Spain 11 September 2019

### Motivation

Read accesses: regular, predictable local reuse

#### Motivation

Read accesses: irregular, short, pattern unknown at compile time

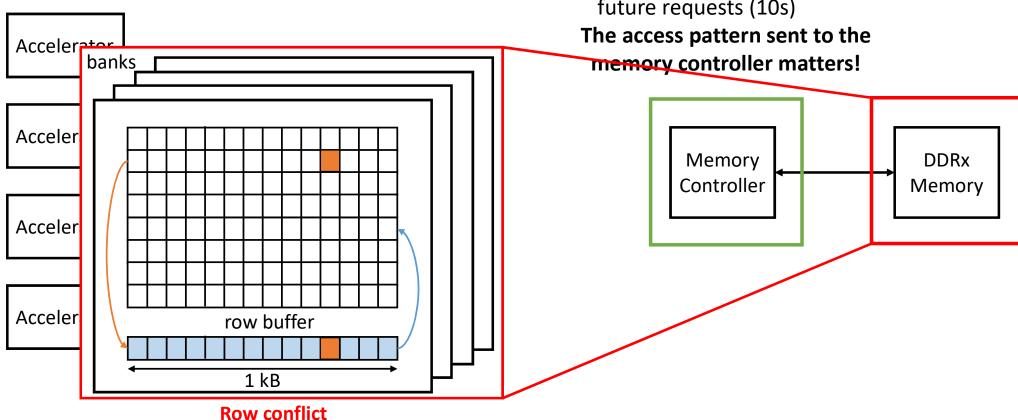

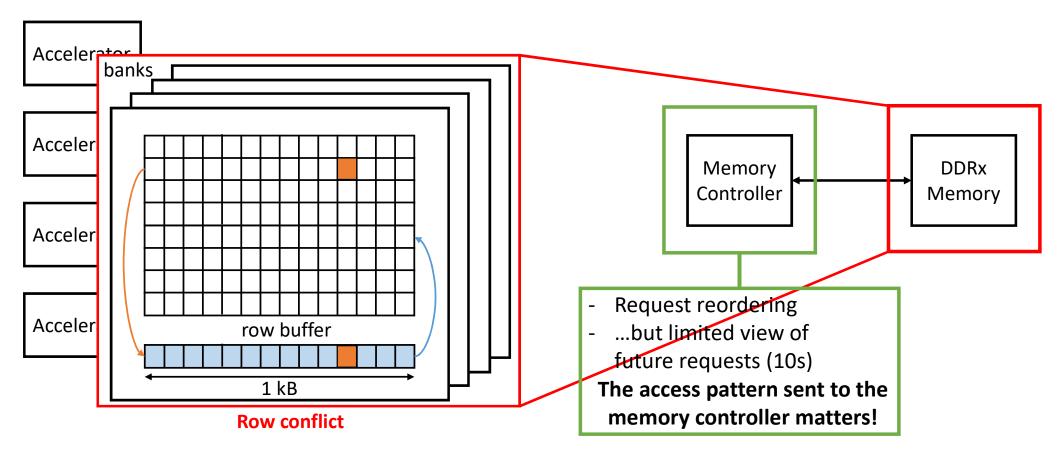

- Request reordering

- ...but limited view of future requests (10s)

5

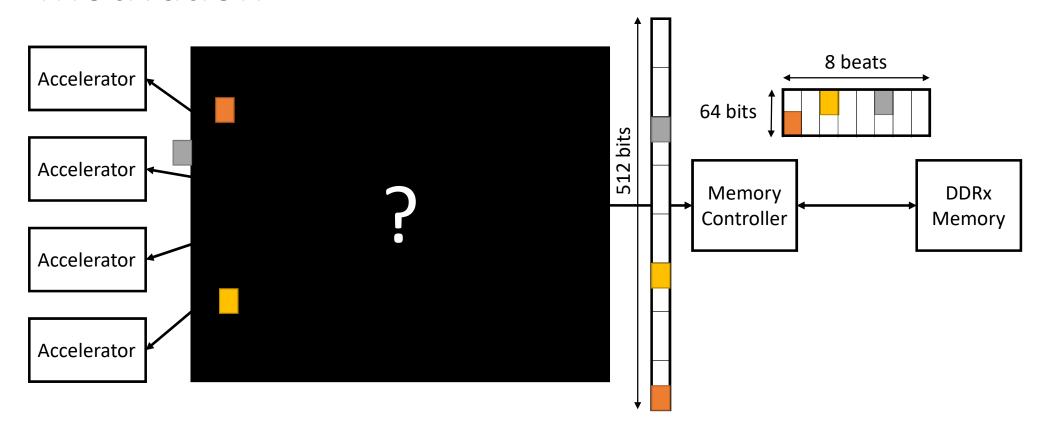

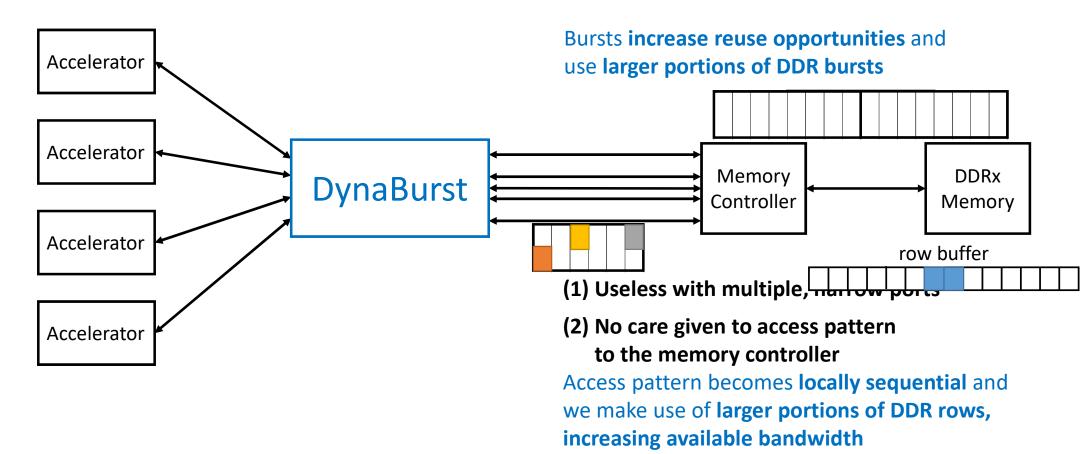

# Key Idea: Bursts of Memory Requests

#### Outline

- Nonblocking Caches and Miss-Optimized Memory Systems

- Top-Level Architecture

- Handling Bursts

- Experimental Setup

- Results

- Conclusion

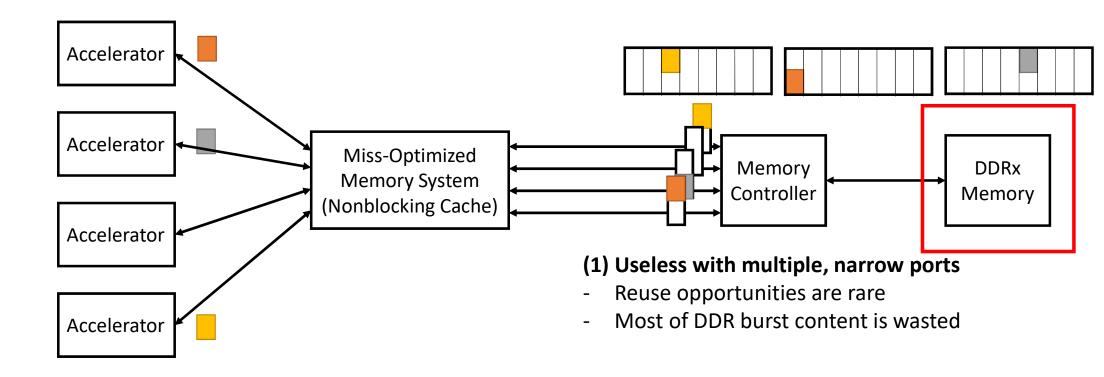

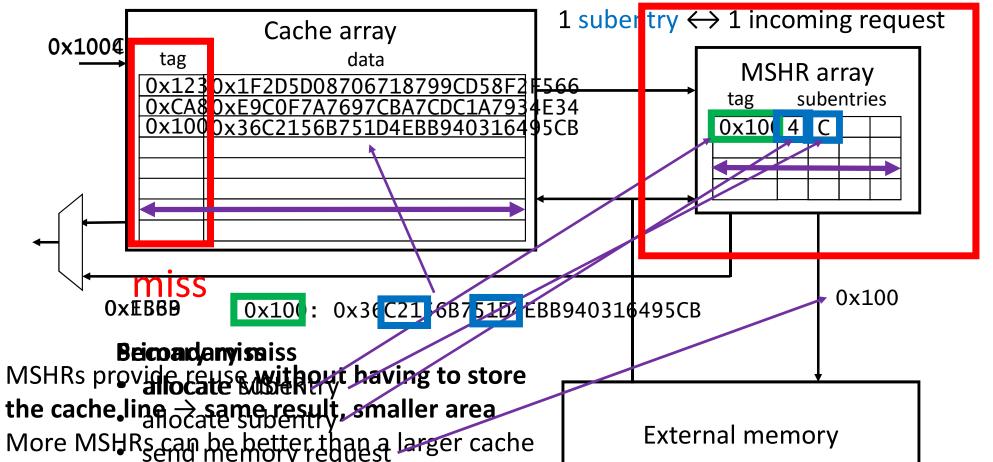

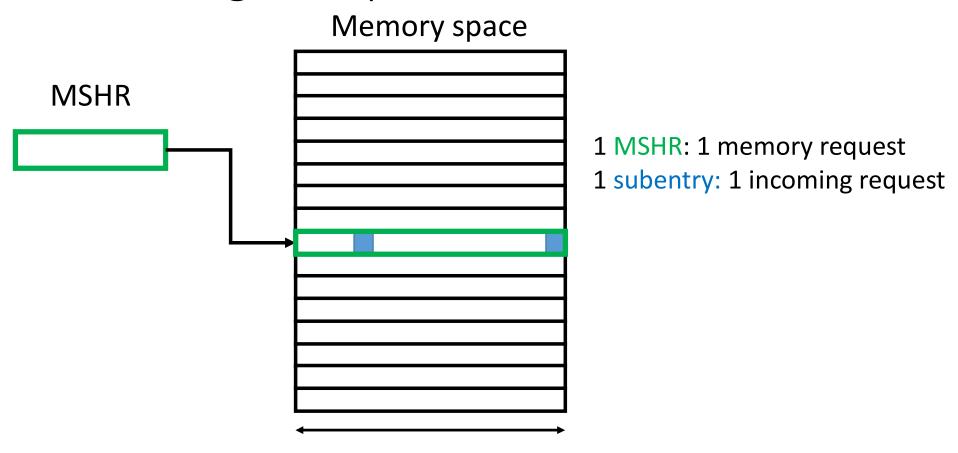

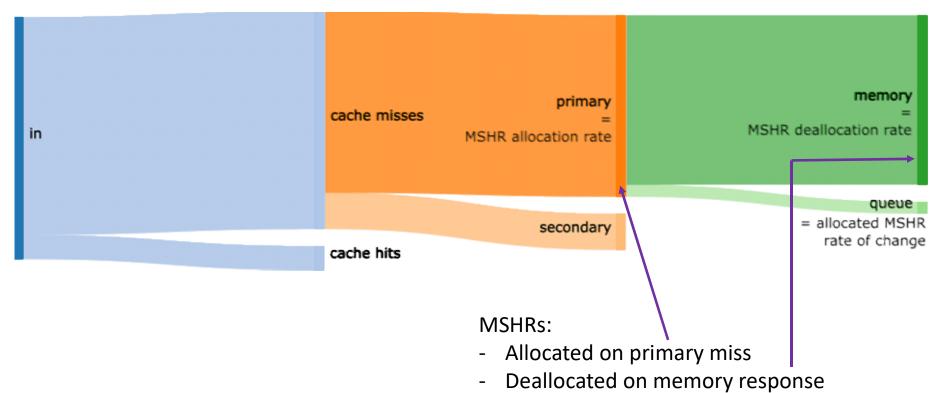

# Nonblocking Caches

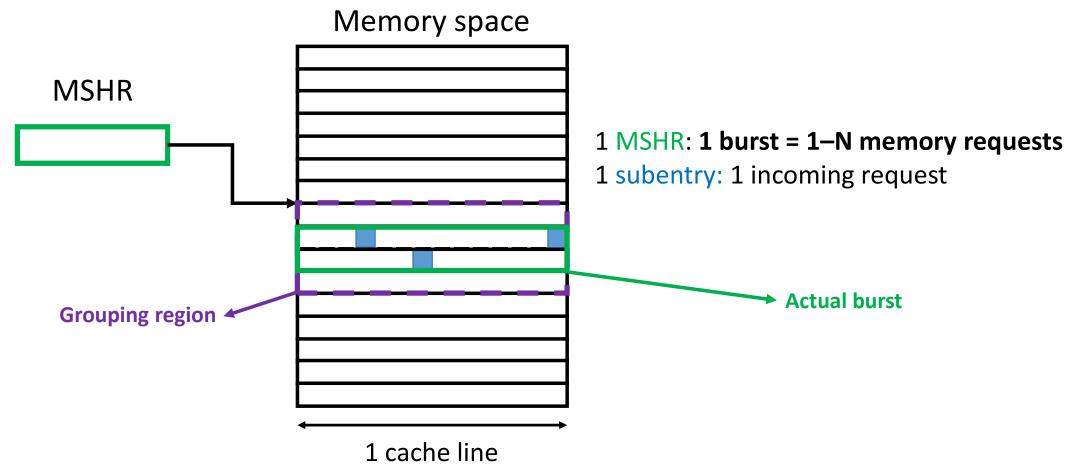

MSHR = Miss Status Holding Register

$1 \text{ MSHR} \leftrightarrow 1 \text{ memory request} = 1 \text{ cache line}$

# Scaling Up Miss Handling

#### **Traditional nonblocking caches**

#### **Miss-Optimized Memory System [1]**

→ efficient storage and lookup of 10,000s MSHRs and subentries

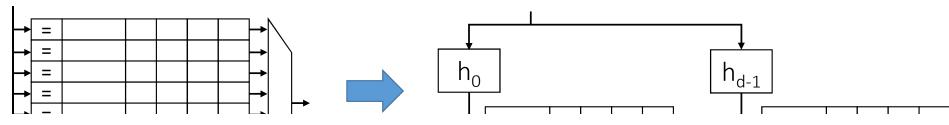

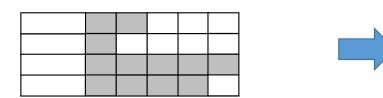

#### **Fully-associative array**

Subentry slots statically assigned to MSHRs

#### **Cuckoo hash tables in BRAMs**

**Dynamic subentry allocation**

#### Outline

- Nonblocking Caches and Miss-Optimized Memory System

- Top-Level Architecture

- Handling Bursts

- Experimental Setup

- Results

- Conclusion

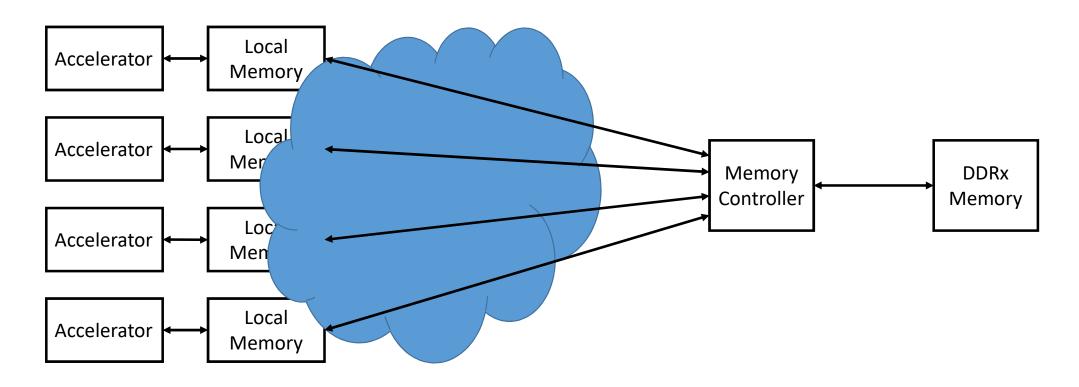

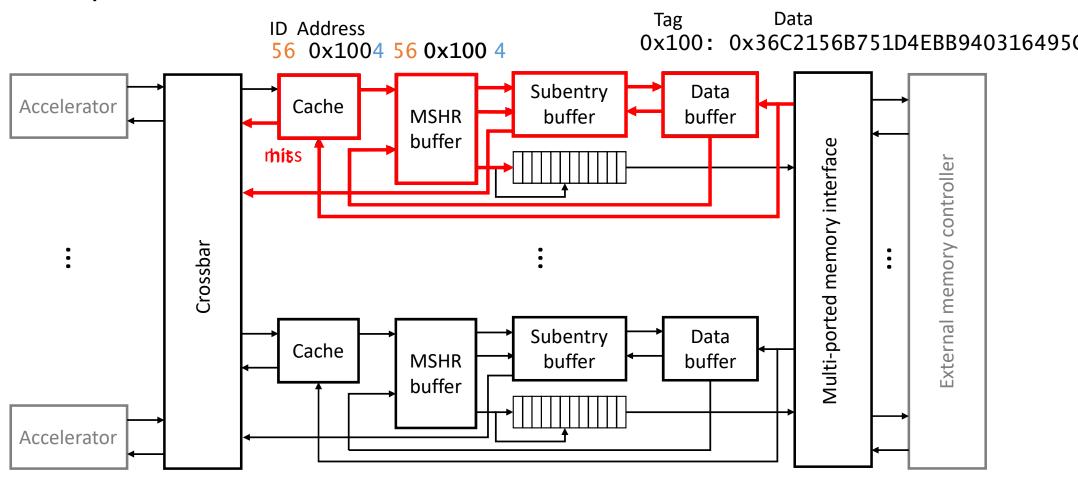

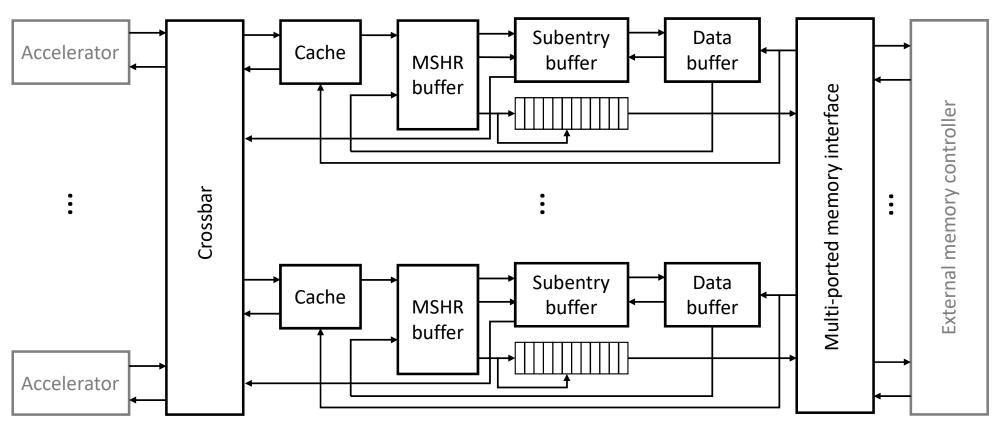

# Top-Level Architecture

# What's New in DynaBurst

#### Variable-length burfseps → LUTRAMIți BRANdd

#### Outline

- Nonblocking Caches and Miss-Optimized Memory System

- Top-Level Architecture

- Handling Bursts

- Experimental Setup

- Results

- Conclusion

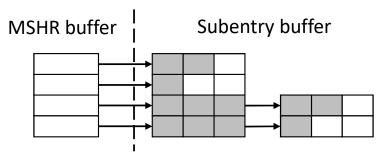

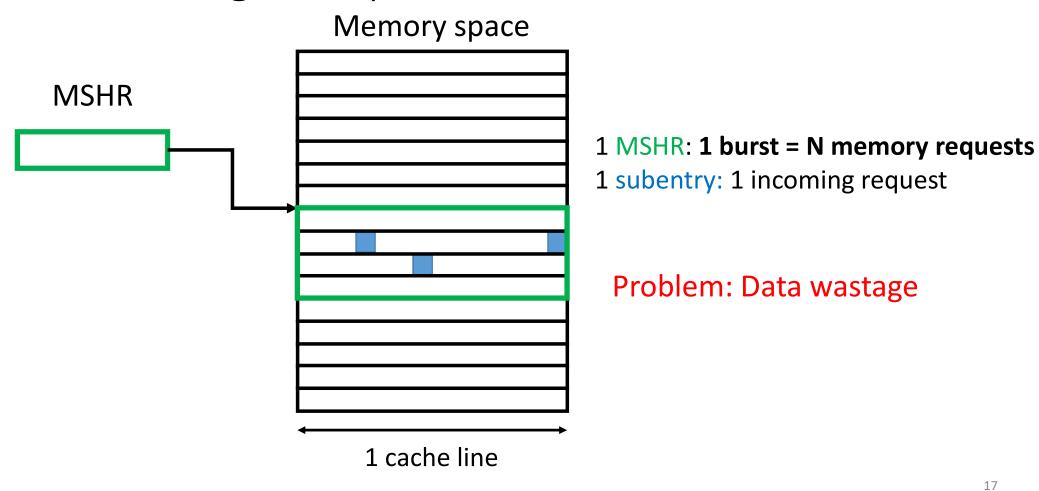

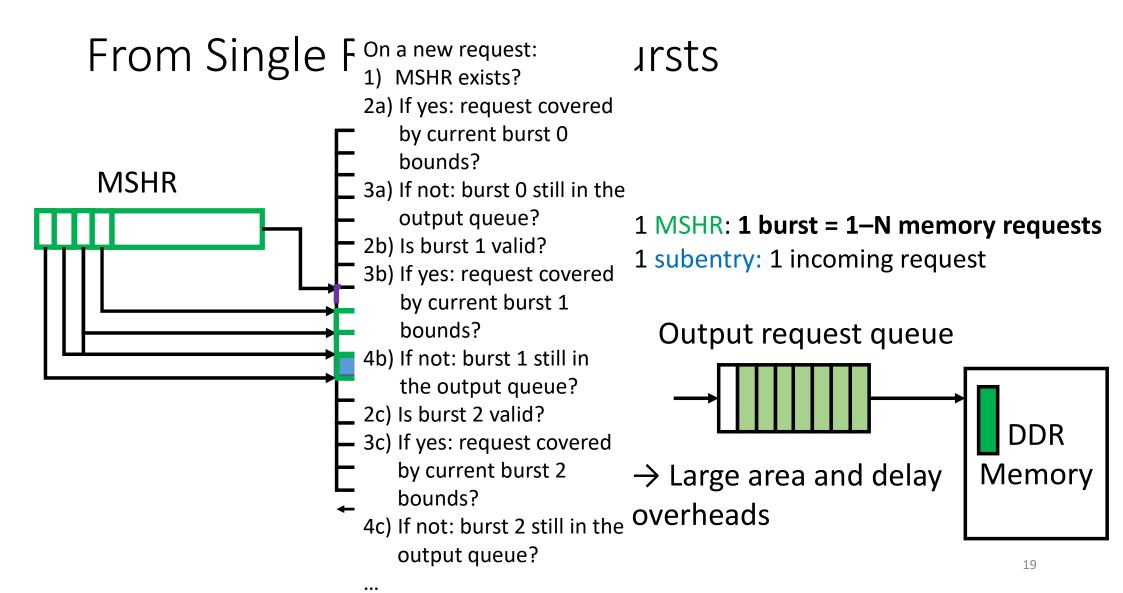

# From Single Requests to Bursts

# From Single Requests to Bursts

## From Single Requests to Bursts

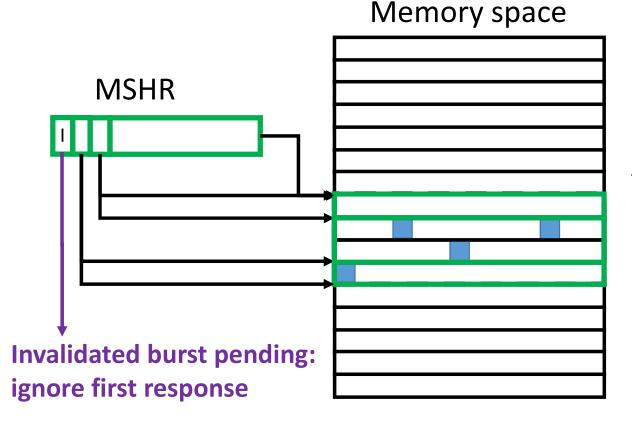

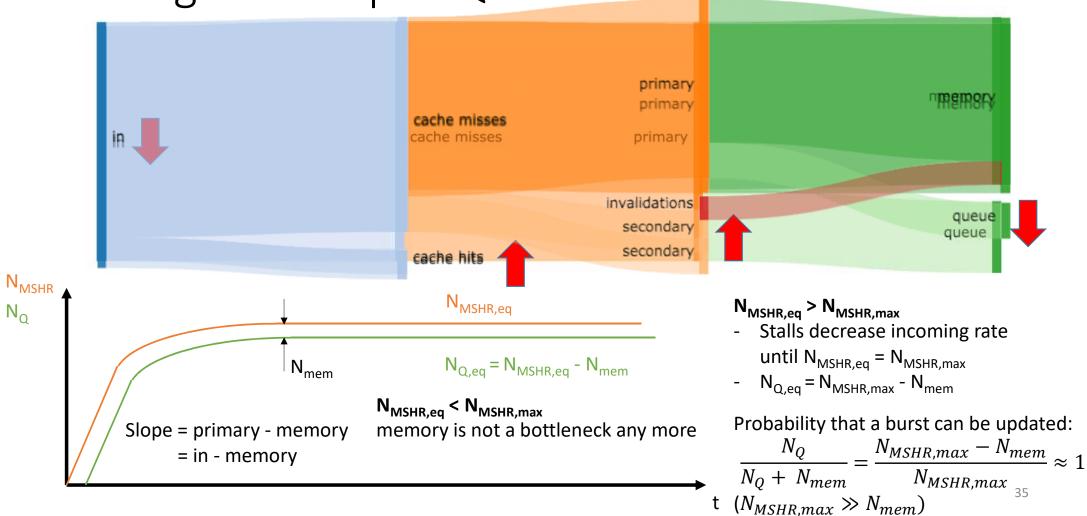

#### **Burst Invalidations**

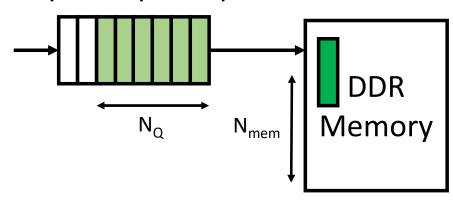

Burst updatable during

$$\frac{N_Q}{N_Q + N_{mem}}$$

of its lifetime

Capacities:

Queue:  $\approx 1,000 - 10,000$

Merble Ry pibaliste = 4-10 me00ory requests

$1 \frac{1 \text{ subsentry}}{N_Q + N_{mem}} 1_1 in coming request$

Output request queue

#### Outline

- Nonblocking Caches and Miss-Optimized Memory System

- Top-Level Architecture

- Handling Bursts

- Experimental Setup

- Results

- Conclusion

#### Board: Xilinx ZC706

- XC7Z045 Zynq-7000 FPGA

- 1 GB of DDR3 on processing system (PS) side

- 3.9 GB/s through **four 64-bit ports** at 150 MHz

- 1 GB of DDR3 on programmable logic (PL) side

- 12.0 GB/s through one 512-bit port at 200 MHz

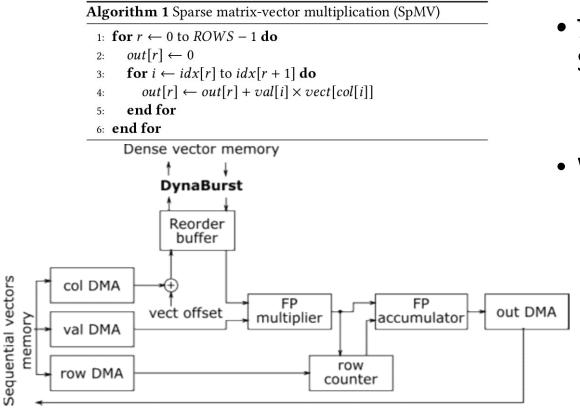

# Accelerators: Compressed Sparse Row SpMV

- 15 sowock in adtsafrout Spitte Speatse SpMHclude web, social, road

- Met vaior kor ange niere an prohiteratumaning

- 59 grecision floating point

- Whyasuphylv?

- Kepteseritative of PateM By-tolerant, (கொக்Widtheb வெளி இடு)ications with various degrees of locality

- Important kernel in many applications

- Several sparse graph algorithms can be mapped to it

A. Ashari et al. "Fast Sparse Matrix-Vector Multiplication on GPUs for graph applications" SC 2014

| https://articles.com/articles.com/scape Matrix-Vector Multiplication on GPUs for graph applications" SC 2014

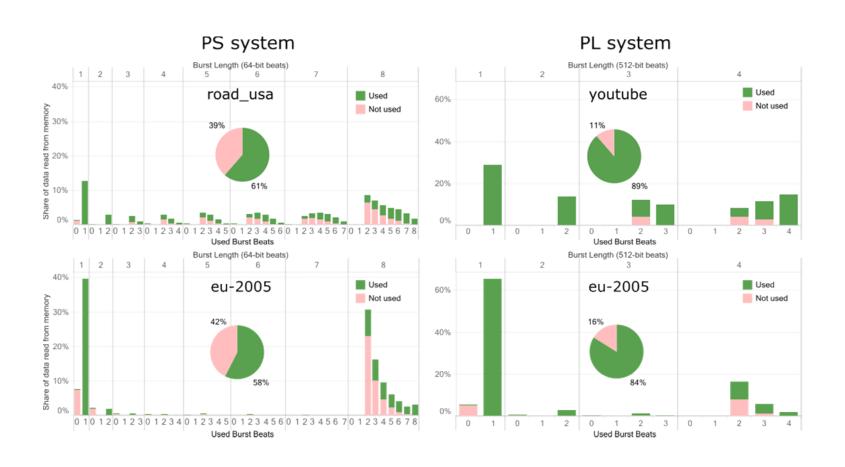

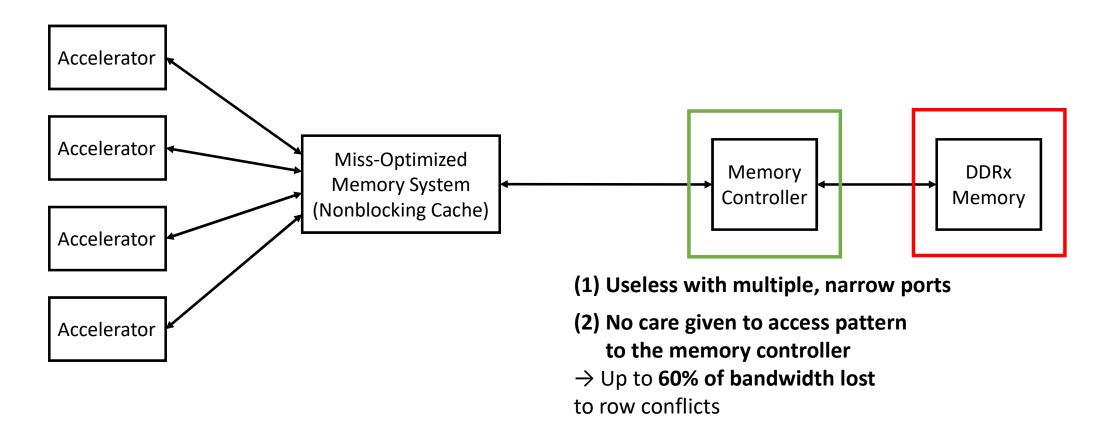

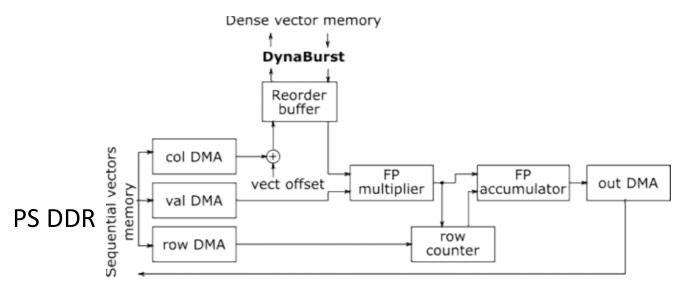

# PL and PS Systems

High bandwidth, single wide port PL DDR

Low bandwidth, 4 narrow ports

#### **PL** system

- Same as in our previous work

- 4 accelerators and banks

- 200 MHz

#### **PS** system

- 8 accelerators and banks

- 150 MHz

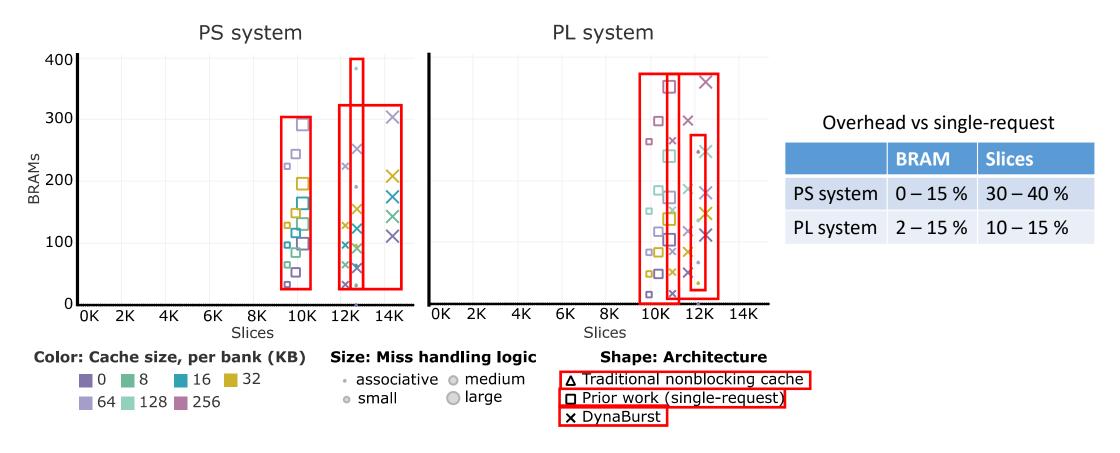

# Design Space Exploration

|                                  | PL systems (4 banks)     | PS systems (8 banks)     |

|----------------------------------|--------------------------|--------------------------|

| Total cache size (KB)            | 0, 128, 256, 512, 1024   | 0, 64, 128, 256, 512     |

| Maximum burst length             | 2, 4, 8, 16              |                          |

| Miss handling (6 subentries/row) |                          |                          |

| - Small                          | 2k MSHR, 12k subentries  | 4k MSHR, 24k subentries  |

| - Medium                         | 6k MSHR, 48k subentries  | 8k MSHR, 48k subentries  |

| - Large                          | 16k MSHR, 96k subentries | 16k MSHR, 96k subentries |

- Baselines: other generic memory systems for irregular access pattern

- Our prior work (single-request)

- Each design point compared to same cache and miss handling configuration

- Traditional nonblocking cache with associative MSHRs

- 16 MSHRs + 8 subentries each, per bank

- Each design point compared to traditional cache with closest BRAM utilization

#### Outline

- Nonblocking Caches and Miss-Optimized Memory System

- Top-Level Architecture

- Handling Bursts

- Experimental Setup

- Results

- Conclusion

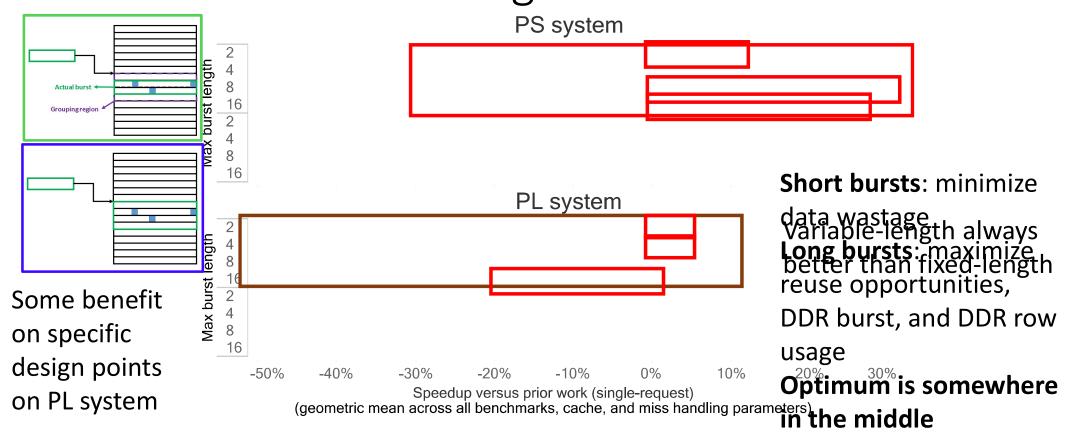

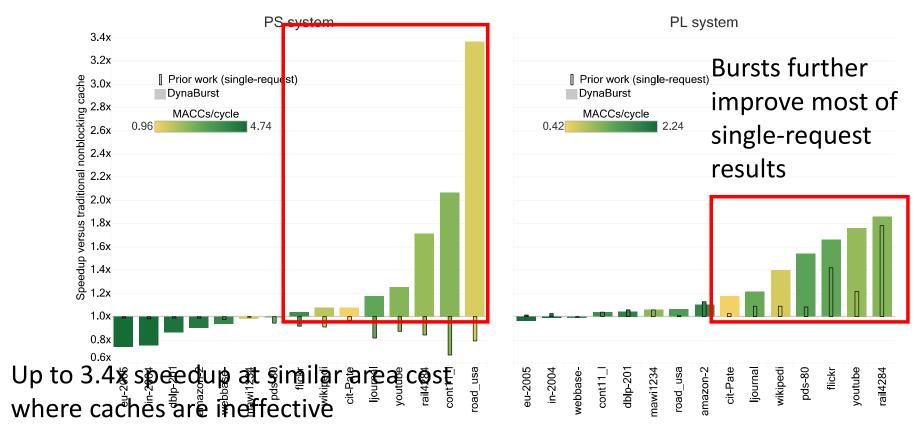

# Impact of Maximum Burst Length and of Burst Trimming

Bursts much more useful on PS system

We'll now consider only best max burst lengths

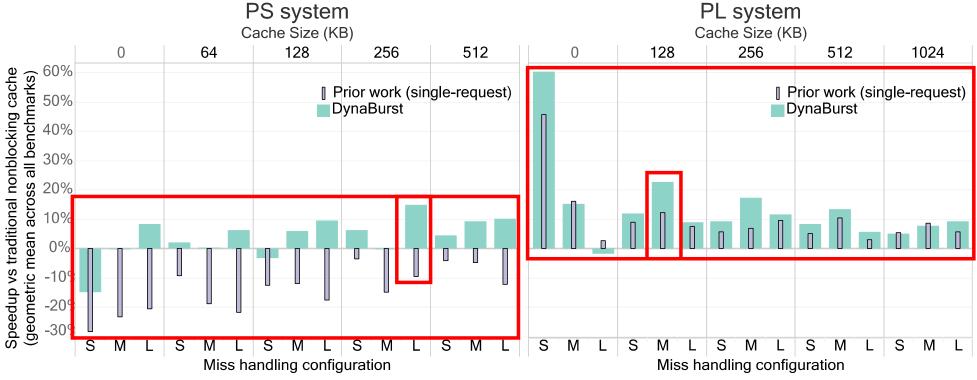

# Cache and Miss Handling Size Exploration

Bursts required to make miss-optimized memory systems cost-effective

Bursts further improve performance on most of the design points

We'll now look into these points

# Speedup on Individual Benchmarks

Most effective where traditional cache performance was lower

#### Resource Utilization

#### Conclusion

- Caches are not effective when read accesses are irregular and short

- Single-request miss-optimized memory systems

- Reuse same memory request among multiple incoming requests

- Useful only when memory controllers have wide ports

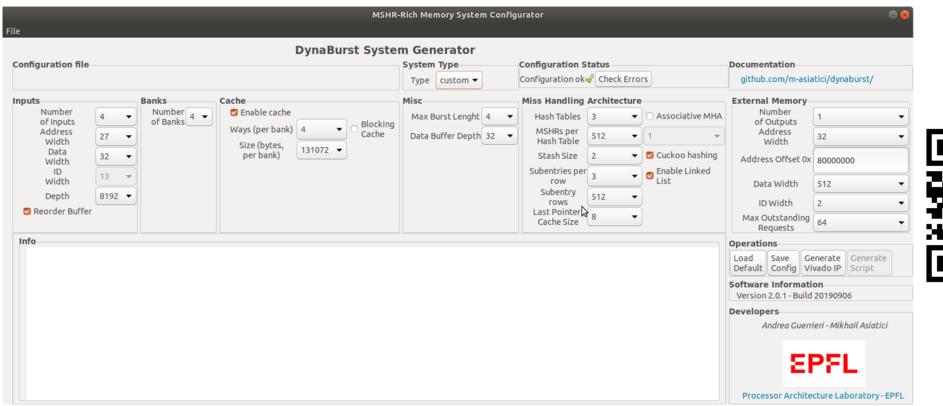

#### DynaBurst

- Merges incoming requests into **bursts** of memory requests

- Controller with narrow ports: up to 3.4x speedup compared to cache with similar area

- Controller with wide port: up to 2.4x speedup with < 15% area overhead compared to prior work

# Thank you!

https://github.com/m-asiatici/dynaburst

# Backup

# Filling the Output Queue

#### Memory bound $\rightarrow$ in > memory

Memory response rate = memory request rate

Filling the Output Queue

# Invalidations and Burst Usage